Why PCIe 7.0 Matters Right Now

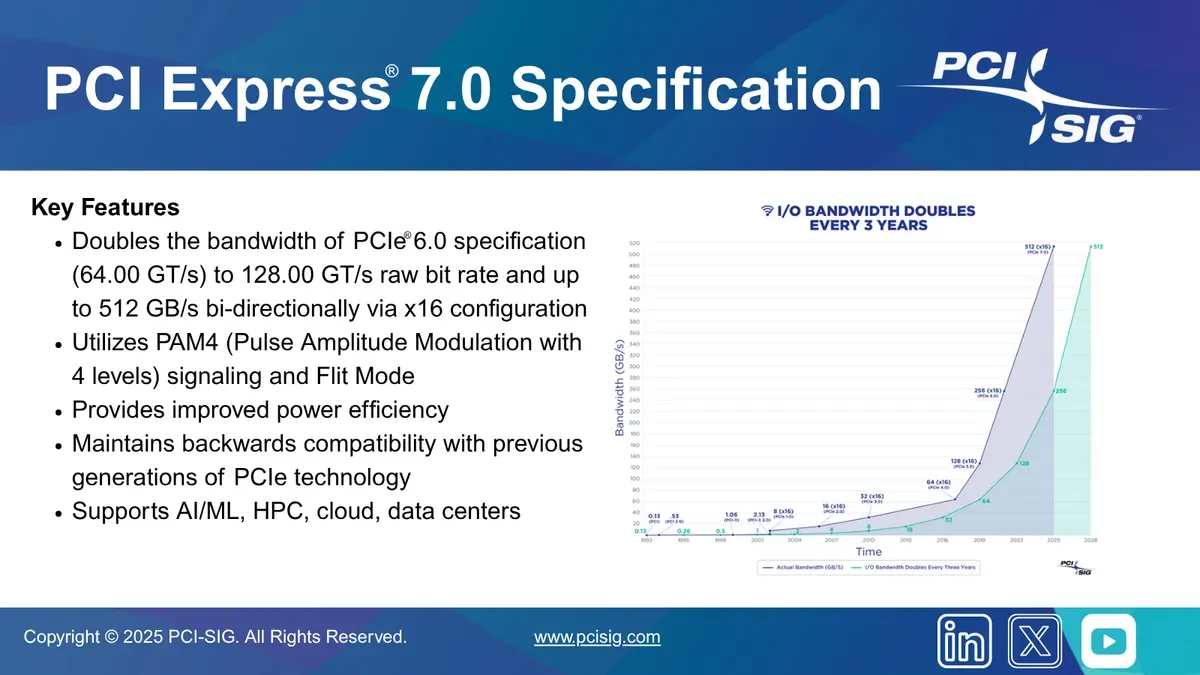

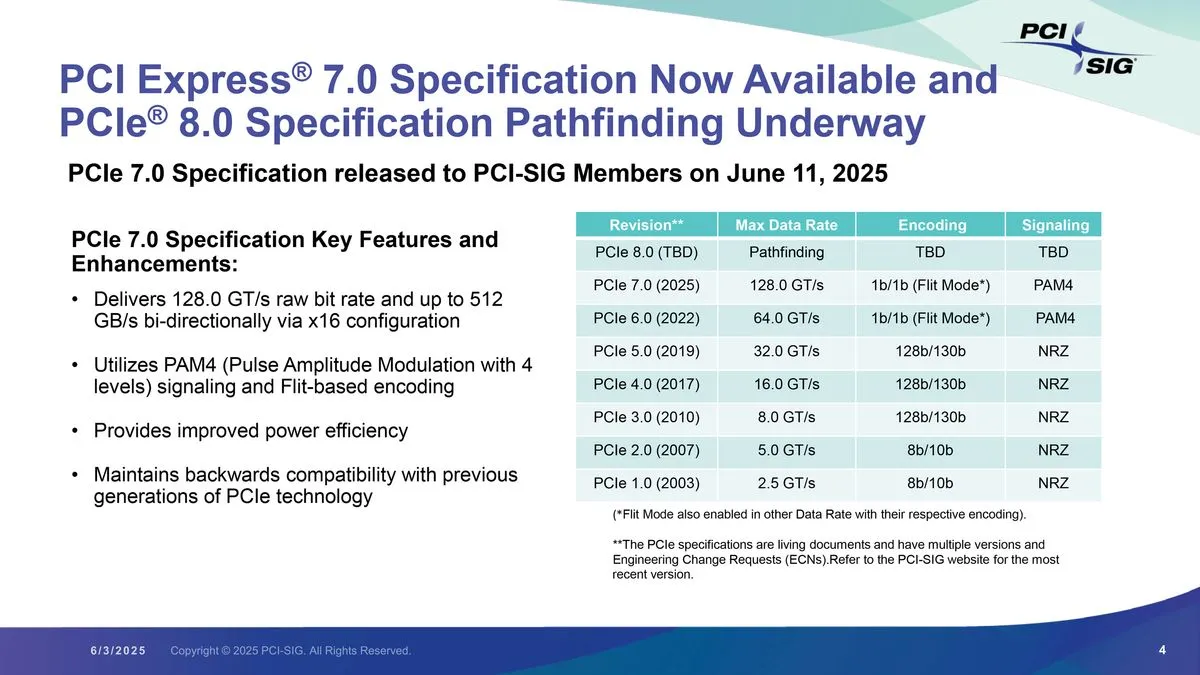

First time I saw a demo of PCIe 7.0 at Computex, my jaw flat-out dropped. The engineer pushed a terabyte file across a single slot in under two seconds—then calmly asked if I wanted coffee. I’d spent the previous weekend waiting on a sluggish RAID rebuild, so yeah, I almost cried. PCIe 7.0 isn’t just a speed tweak; it’s a paradigm shift. We’re talking 128 GT/s per lane raw, a mind-bending 512 GB/s full-duplex on x16, and (drumroll) industry-standard optical interconnect baked straight into the spec. If you build servers, crunch AI models, or just hate load screens, buckle up—because this bus is gonna fly.

PCIe 7.0 at a Glance

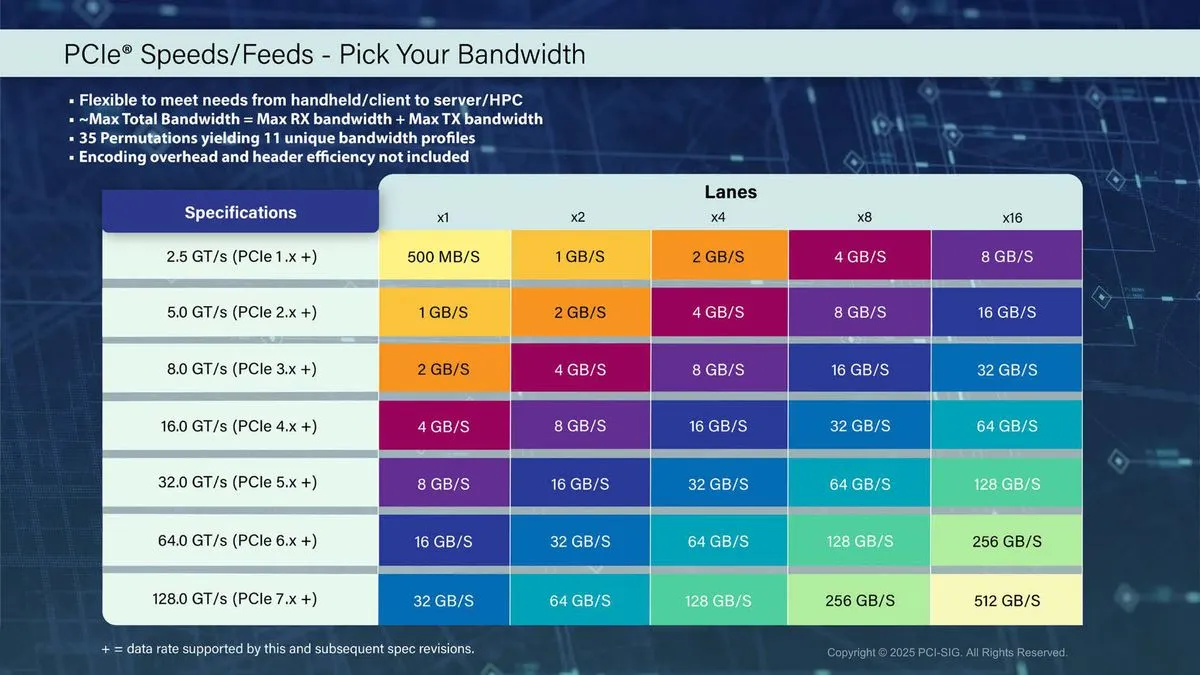

| Generation | Raw Rate (GT/s) | x16 Duplex Bandwidth | Encoding | First Products |

|---|---|---|---|---|

| PCIe 3.0 | 8 | 32 GB/s | 128b/130b NRZ | 2012 |

| PCIe 4.0 | 16 | 64 GB/s | 128b/130b NRZ | 2019 |

| PCIe 5.0 | 32 | 128 GB/s | 128b/130b NRZ | 2021 |

| PCIe 6.0 | 64 | 256 GB/s | PAM4 + FLIT | 2024 |

| PCIe 7.0 | 128 | 512 GB/s | PAM4 + FLIT 2.0 | 2028 (est.) |

See that doubling cadence? PCI-SIG promised “every three years,” and they’ve mostly nailed it for two decades straight. PCIe 7.0 continues the trend—while layering in optical mojo we’ll dig into soon.

(Image credit: PCI-SIG)

The Science Behind 128 GT/s

PAM4: More Bits per Wiggle

Plain old NRZ signaling tops out near 32 GT/s before eye-diagrams look like spilled spaghetti. PCIe 7.0 leans on Pulse-Amplitude Modulation 4 (two bits per symbol) to double throughput without doubling frequency. Eye openings shrink, but advanced DSP and equalization keep them clean enough to party.

FLIT 2.0 Encoding

Fixed-length Flow Control Units chop transactions into lean 256-byte slices—less overhead, better error containment, slicker QoS. Think of FLITs as pre-measured espresso shots: tidy, potent, predictable.

# Quick Linux sanity check

sudo lspci -vv | grep "LnkSta:"

# When PCIe 7.0 boards arrive, look for '128 GT/s'Kicking Copper to the Curb: Optical Links

Let’s be real—copper traces are awesome until they aren’t. At tens of gigatransfers, they radiate heat, jitter like mad, and guzzle power for re-drives. PCIe 7.0 introduces an optical-aware retimer spec: tiny SoCs that flip electrical into light, blast it across fiber, then flip it back—latency under 5 ns hop-to-hop. Goodbye EM interference, hello rack-scale bandwidth.

- Bandwidth ceiling: single-mode fiber laughs at 128 GT/s, scaling to multi-terabit with wavelength division.

- Power profile: early prototypes sip <5 pJ/bit, roughly 1/10 power of equalized copper over 2 m.

- Reach: 100 m inside data centers without repeaters—goodbye expensive active copper cables.

Need receipts? Check the AnandTech deep dive or Tom’s latest engineering breakdown.

(Image credit: PCI-SIG)

Power, Thermals & Backward Love

You’d think doubling speed doubles watts—nope. By leaning on PAM4 and smarter equalizers, PCIe 7.0 targets 15-20% better perf-per-watt versus 6.0. And yes, it remains fully backward compatible. Your crusty Gen-3 SSD will still enumerate; it’ll just crawl in the ultra-fast lane like grandma on Sunday.

Real-World Workloads That Crave PCIe 7.0

AI & Machine Learning

Training 100-billion-parameter models means GPU clusters scarf bandwidth like teens scarf pizza. Slot-to-slot PCIe 7.0 lets eight GPUs trade gradients at wire speed, shaving multi-week training runs down to days.

High-Performance Compute

Climate sims, drug discovery, you name it—HPC codes juggle petabytes. NVMe-oF fabrics over PCIe 7.0 will feed hungry compute nodes without resorting to pricey proprietary interconnects.

Consumer Perks

- 8K 120 Hz VR streaming with zero tearing.

- Local LLM inferencing on next-gen GPUs without bus bottlenecks.

- Optical cables on enthusiast boards = cooler, cleaner builds.

(Image credit: PCI-SIG)

Roadblocks & Rollout Timeline

Nothing this fast comes easy.

- Cost: PAM4 serdes and photonics aren’t budget parts—expect price bumps first wave.

- Testing gear: Signal analyzers that hit 70 GHz ain’t cheap; OEM validation costs rise.

- Supply chain: Co-packaged optics need new assembly lines; ramp starts 2027.

According to PCI-SIG’s own roadmap, compliance test fixtures ship late 2026, with data-center NICs landing 2028. Consumer boards? 2029 holidays if history rhymes.

What Enthusiasts & Builders Should Prep For

Action items while you wait:

- Upgrade PSU headroom—future GPUs on PCIe 7.0 may spike harder.

- Plan your case routing—optical jumpers bend differently from copper.

- Bookmark these deep dives: our Apple M5 Chip breakdown (massive PCIe lane appetite) and the DDR5 vs DDR4 guide for balanced builds.

Final Take

I’m gonna say it: PCIe 7.0 feels like moving from a two-lane backroad to a fiber-optic autobahn. The spec nails speed, slices power, and future-proofs our rigs with light. Sure, wallets will sting at first and firmware devs will curse new error codes, but once you copy a 500 GB game in four seconds flat you’ll never look back. I’m already clearing a spot on my test bench—coffee stocked, stopwatch ready. See you in the fast lane.

FoxDoo Technology

FoxDoo Technology